Guest article written by Kumar Abhishek on the Octavo Systems website:

BeagleLogic Standalone – Featuring the OSD3358-SM

Three years ago, as a student under the Google Summer of Code program for BeagleBoard.org, I developed BeagleLogic – that turned the BeagleBone Black and its variants into a Logic Analyzer using the Programmable Real-Time Units (PRUs) on the AM335x SoC to capture up to 14 inputs up to 100 MSamples/sec. It is possible to fill up to 300MB of the 512MB DDR RAM in the BeagleBone with logic samples – that’s 3 seconds of data at 8 channels (1.5 secs at 16 channels). I also designed a cape for the system – called the BeagleLogic cape that would allow buffering the external logic signals up to 5V TTL so that they do not damage the BeagleBone.

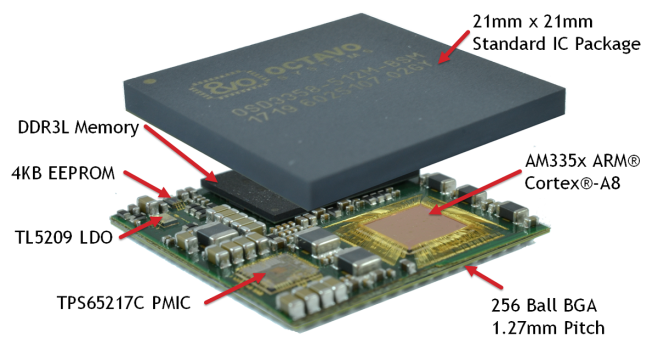

The launch of Octavo Systems and its OSD3358 SiP got me excited, and the idea of a turnkey version of BeagleLogic was rekindled as the design would be greatly simplified due to the SiP integrating the core components, leaving me to focus on the features I want to add to the system.

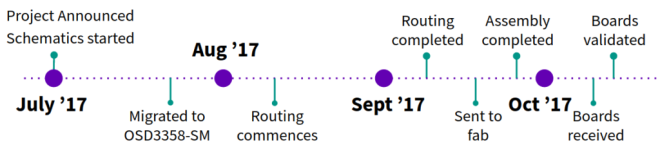

From concept to completion, this project took 4 months working on it part-time. I relocated in August so work happened at an even slower pace during that month

The schematics were originally based on the OSD3358, however Jason encouraged me to design based on the newly announced OSD3358-SM as it was smaller and had a more optimized ballmap. The schematics were then migrated to the OSD3358-SM in late July. At the beginning of the routing exercise, I was really apprehensive if the design could be routed in 4 layers but thanks to the optimized ball map of the OSD3358-SM, the routing was easily completed so.