From the Intelligent Toasters blog:

Retro CPC Dongle – Part 38

This post talks about HyperRAM, what it is, how to interface to it and how to improve the performance of high-speed parallel interfaces. HyperRAM is described well by Cypress. It is essentially a double data rate RAM with a compact 12-line interface that masks the underlying technology of a DDR SDRAM.

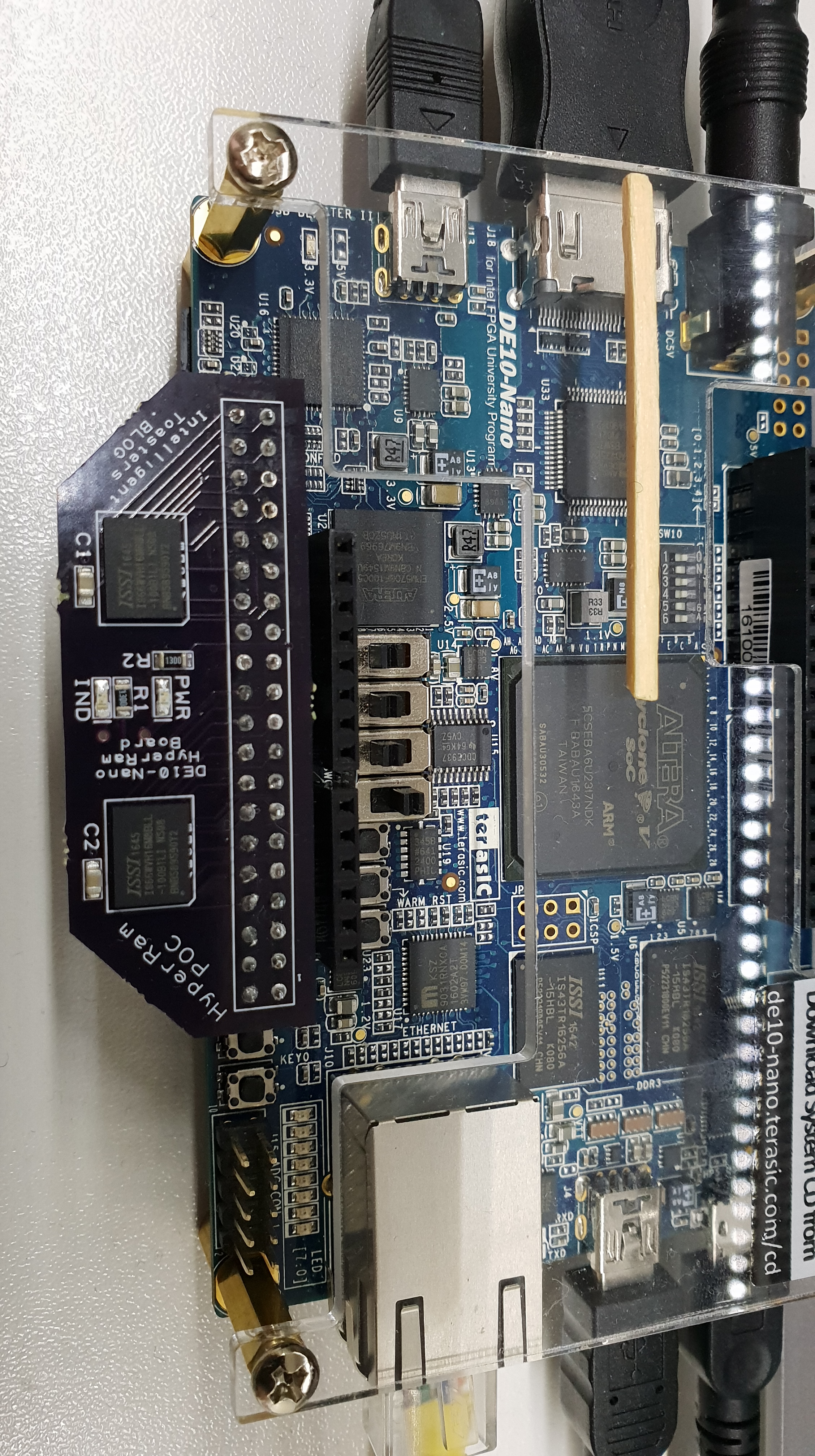

Since assembling the two HyperRAM chips on my new OSH Park prototype boards (above), work on the CPC2 has come on in bounds. This lack of large memory was really holding back progress. I’ve completed the ROM/RAM management cores, so that 64 ROMs and 4096KB of RAM is now available to the CPC2, managed by the support processor. Based on the required CPC personality, I can switch out the CPC464/664/6128 ROMs, the BASIC 1.0/1.1 ROM, the AMSDOS ROM and others like my beloved Maxam ROM. The ROMs are stored in the FPGA configuration Flash. Storing 64 ROMs beyond the FPGA configuration image takes just a small fraction of the Flash memory. As they never change, it’s a good place to hold these. In the future, ROMs will also be stored on the backing storage for more volatile images, such as ROMs under development.