iCEBreaker Production

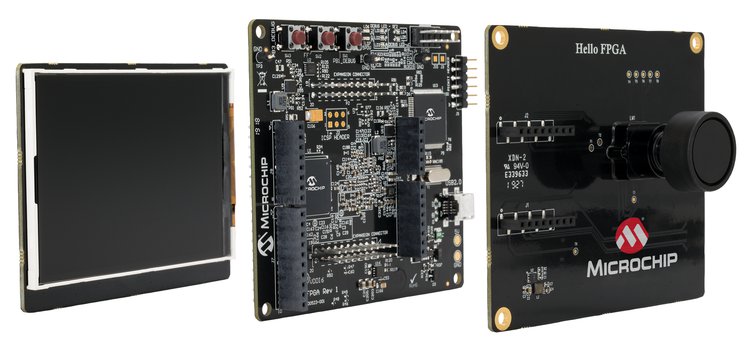

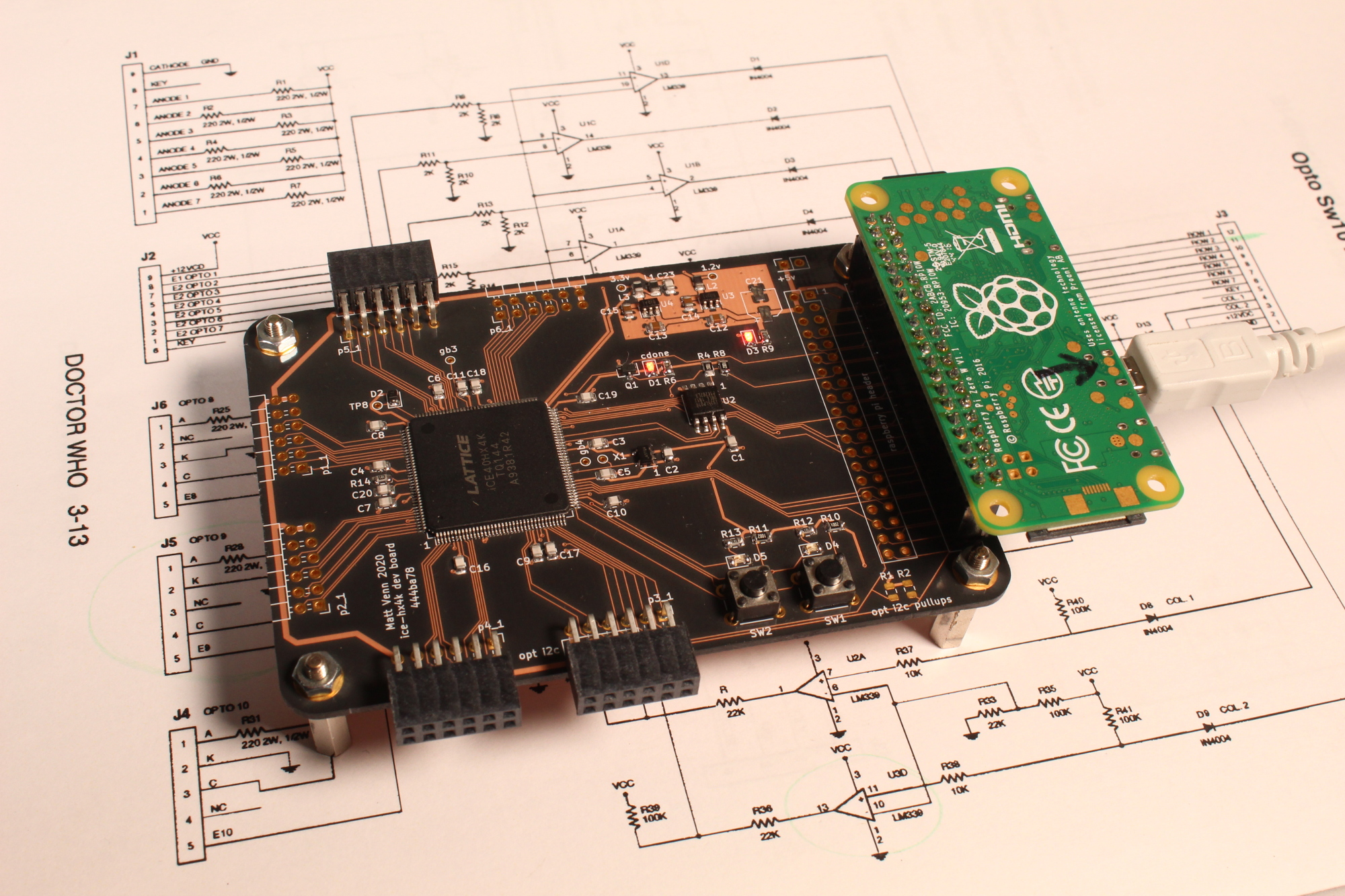

As you read in our last update in November, we finished fulfilling the campaign, but that does not mean work on iCEBreaker has stopped. We keep producing iCEBreakers and Pmods to keep 1BitSquared US and 1BitSquared DE, as well as Crowd Supply and Mouser, stocked.

For those of you who are patiently waiting for your shipments, don’t worry. A package with additional inventory is going out to the Mouser warehouse today!

Continuing Work on iCEBreaker

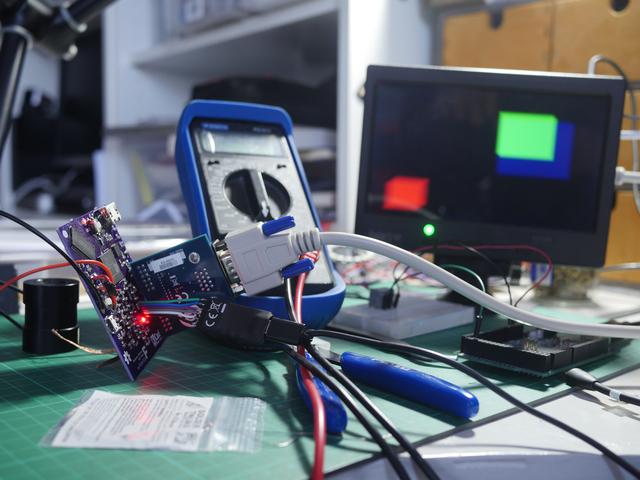

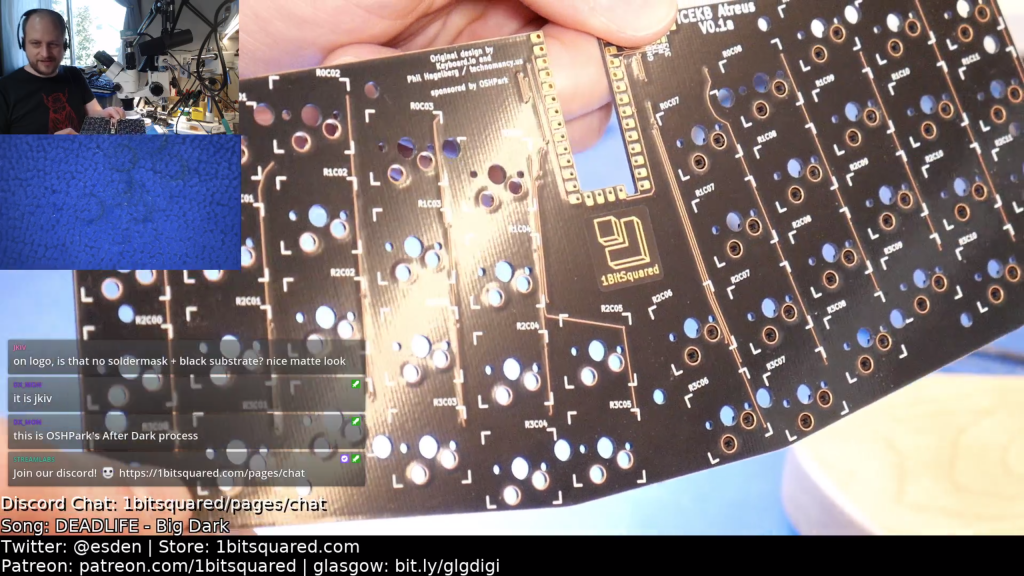

We are continuing work on new examples and additional iCEBreaker hardware. If you are not following 1BitSquared or Piotr on Twitter, you might have missed some stuff that Piotr is working on. Since January, Piotr started streaming on Twitch on a fairly regular basis. You can follow him on Twitch and be notified every time he goes live. Piotr is also announcing upcoming streams at least a day in advance on Twitter as well as on the 1BitSquared Patreon page.

As a result of the Twitch streams, we’ve had a few interesting new developments for the iCEBreaker platform. A few weeks ago, we published Litex RISC-V SOC generation examples that you can find in the iCEBreaker GitHub Organization. Piotr gave a Twitch stream presentation about the build system and how to use it. You can watch the stream Archive on Twitch, diode.zone, and YouTube. This example gives you the foundation to create your own SOC for the iCEBreaker, start adding your custom hardware to the RISC-V core, and program it in C or Rust. We are also working on MicroPython and maybe even CircuitPython support in the not too distant future.

Upcoming Twitch Stream

Piotr has scheduled a Twitch Stream for Tuesday, April 13th, 2020 at noon PDT. He will be working on a new Pmod for the iCEBreaker that will allow us to connect NES or SNES controllers from two very popular 8-bit game entertainment systems. 😉 That same Pmod will also contain a stereo audio output. This Pmod together with a DVI output, LED Panel output or VGA output will be an ideal combination to recreate old or build new custom game consoles and a wide range of emulations, for entertainment, preservation, and education.

If you are curious when the stream will happen in your timezone you can either check on Twitch itself, as there is a countdown timer till the next stream below the video streaming window, or you can check timeanddate.com.

Keep Supporting our iCEBreaker work

If you like to see continuing work and content creation for the iCEBreaker platform, and you already have all the hardware you need, then consider supporting us through Patreon. We keep adding perks for Patrons, like KiCad panel templates and behind the scenes news. We have a few very generous supporters that make the Twitch streams possible, but any additional support is appreciated.

Stay in Touch

And don’t forget, the continuing development and support for iCEBreaker keeps on rolling on the 1BitSquared Discord server, and iCEBreaker forum! So join the fun and show off your iCEBreaker projects! 🙂

Stay safe and healthy,

Piotr and Danika