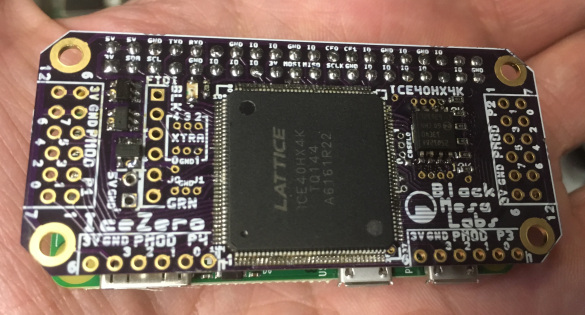

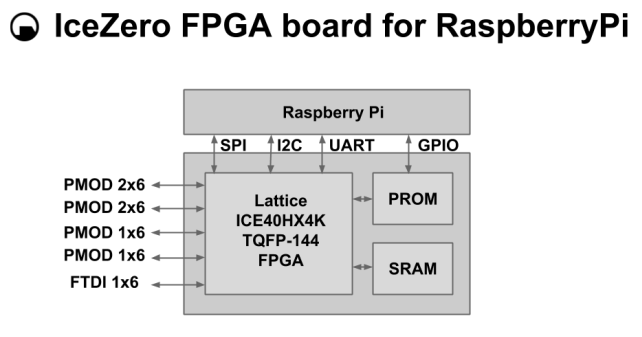

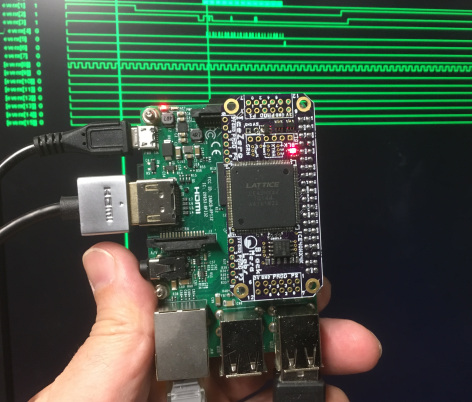

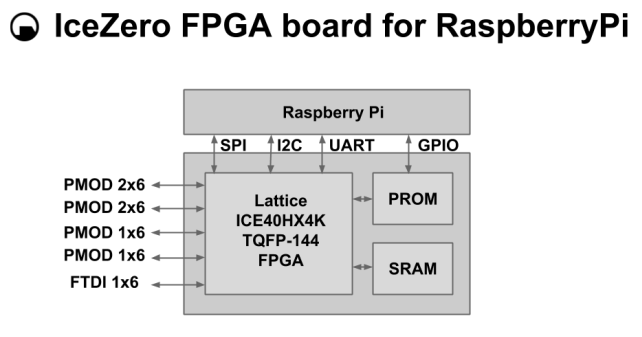

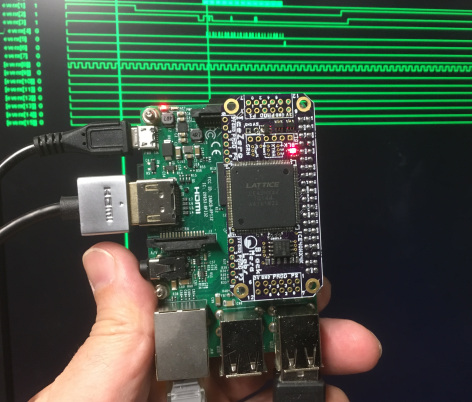

Black Mesa Labs created this board that adds a Lattice FPGA to a Raspberry Pi:

BML has been very much enchanted with the Lattice FPGA boards for Raspberry Pi, IcoBoard , BlackIce and IceHat. The IceZero board is a BML creation that attempts to combine the best features of all 3 boards into a single design.

IceZero features common with other designs

- Fully Open-Source Hardware and Software Design.

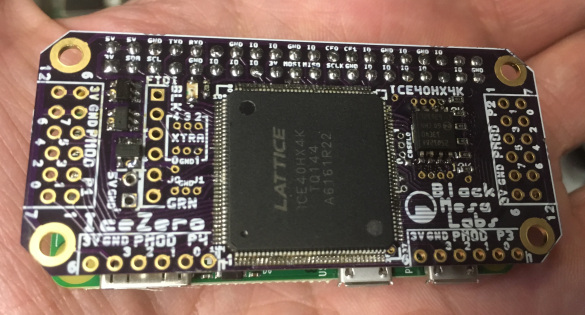

- Lattice ICE40HX4K FPGA that supports Clifford Wolf’s Project IceStorm tool chain.

- Interfaces to Raspberry Pi 2×20 GPIO Header for both power and bus interfaces.

- PROM programmable directly from Rasp Pi, no JTAG programmer required.

- External SRAM, supporting soft CPU core designs ( code execution ).

- Extra large SPI PROM, supporting soft CPU core designs ( code storage ).

- Industry standard PMOD expansion headers

IceZero features that are BML specific

- Mesa Bus Protocol 32 MHz SPI link between CPU and FPGA.

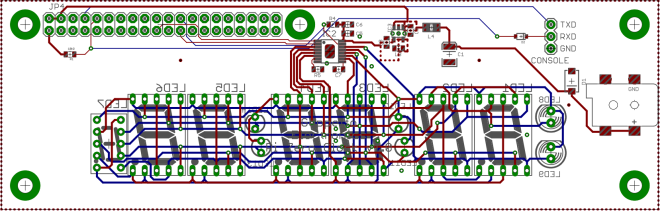

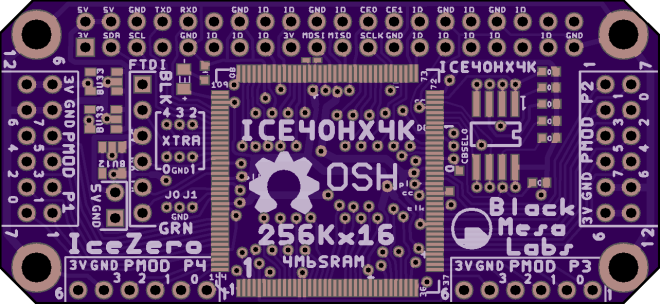

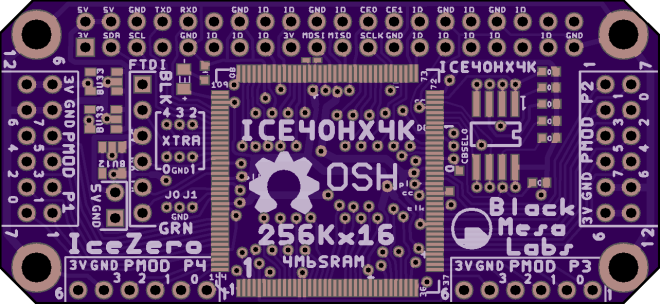

- 2-Layer PCB design. Orderable via OSH-Park or Gerbers for Downloading.

- FTDI 1×6 USB Serial Cable header for use with PC instead of Pi ( or as a soft CPU debug Trace Port ).

- Single Pi UART plumbed to FPGA for muxing to multiple external serial devices.

BlackMesaLabs has shared the board on OSH Park:

BML IceZero Lattice ICE40 FPGA for RaspPi

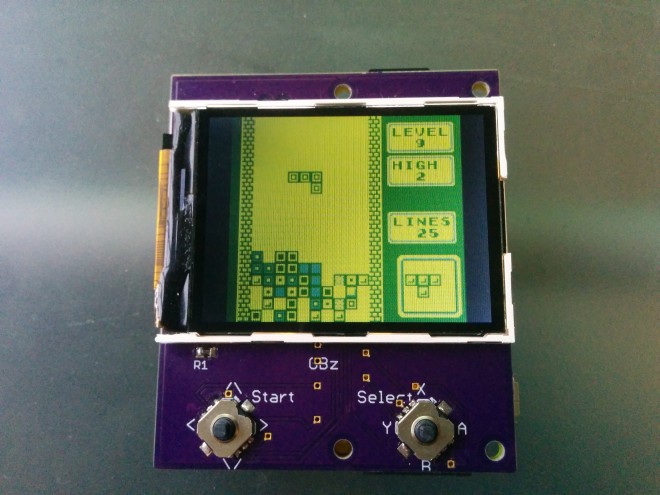

GameBoy Zero, but smaller!

GameBoy Zero, but smaller!