Great Twitter thread from our friend Eric Schlaepfer of TubeTime.us:

“A short but highly technical history of DRAM – dynamic random access memory!”

but first: dynamic?

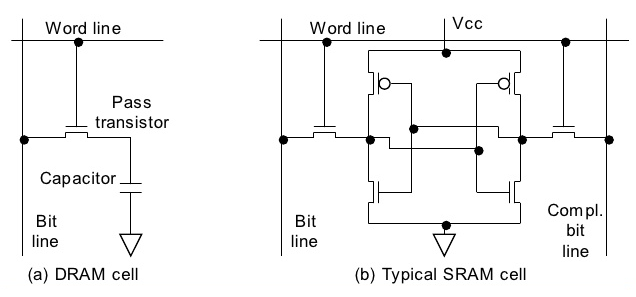

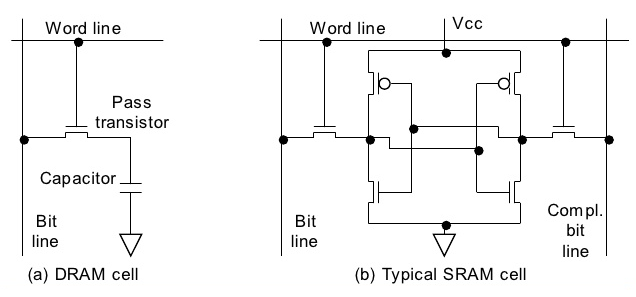

static – a logic circuit that operates down to 0Hz clock.

dynamic – a logic circuit with a minimum clock frequency.static RAM is made of two cross-connected inverters along with two pass gate transistors that connect and disconnect the memory cell to the bit lines. you need 6 transistors to make a cell that can store one bit of information.

dynamic RAM cheats a little and uses a capacitor to store the bit instead. over time, this charge drains away so you have to periodically read the current state and then write it back again. it’s like refilling a leaky bucket.

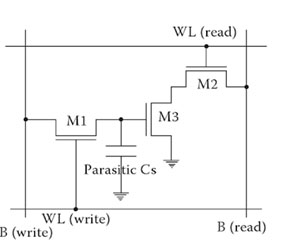

here’s a more detailed diagram of the basic DRAM cell (3 transistor). the bit is stored in the gate capacitance of transistor M3 (shown as “parasitic C”). M1 is closed to write to the cell and M2 is closed to read from the cell.

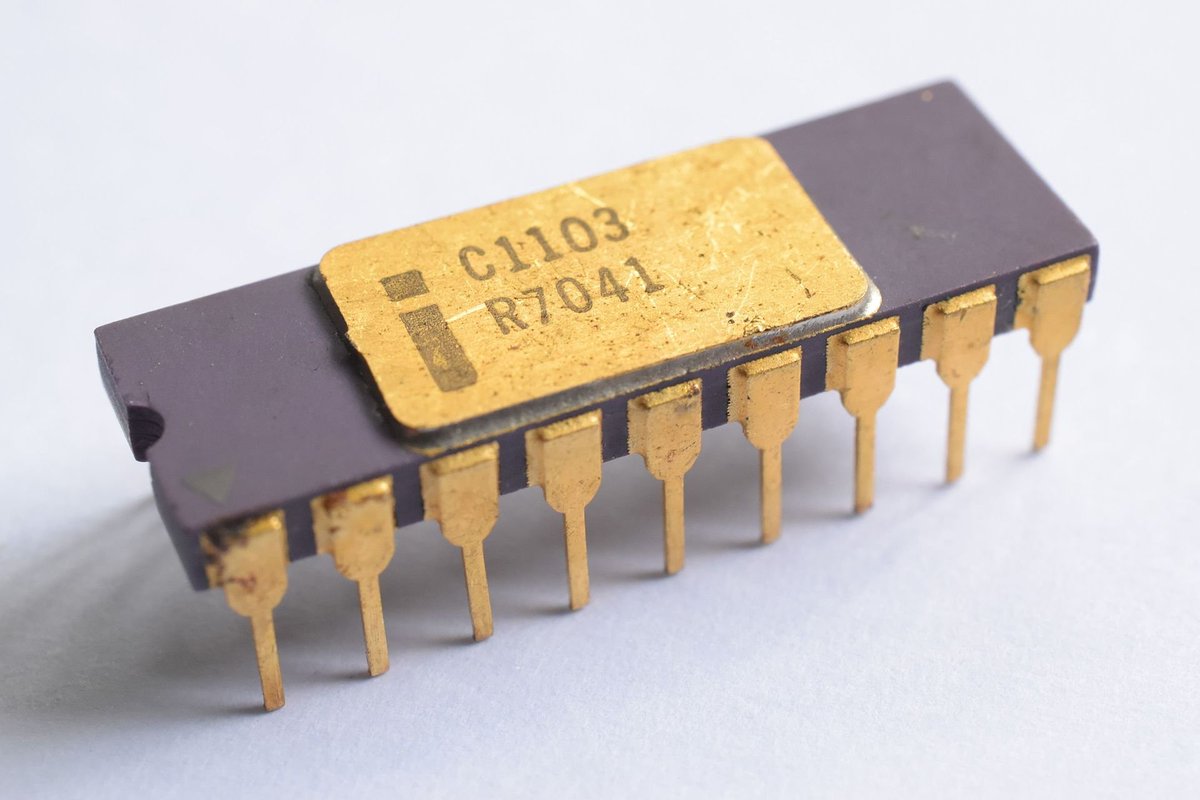

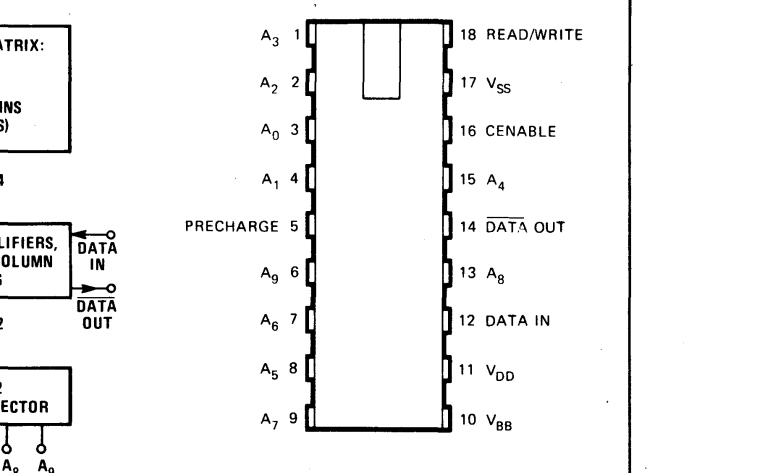

now back to the history: this is the first practical DRAM chip, the Intel 1103, which they introduced in 1970. it was expensive at 1 cent per bit (1024 bits total). that’s about $7 now. you’d need two of these chips to store the text in this tweet!

here’s the pinout. address lines, chip enable, data out (inverted?), data in, read/write, precharge (similar to a clock line), and then three (!) power rails: VSS=+16V!, VDD=GND (PMOS is weird) and VBB=+19.5V(!!!)

Originally tweeted by Tube Time (@TubeTimeUS) on February 27, 2021.